The NJU26103 is a high performance 24-bit digital audio processor for TV that has a QFP 32-pin small package.

The NJU26103 provides an internal delay memory to adjust the output delay time for lip sync. Moreover, the NJU26103 adopts SRS WOW technology.

## FEATURES

- Variable 2 Channels Audio Delay (16 bit data width). Maximum Delay 42msec at Fs = 48kHz (46msec at Fs = 44.1kHz)

- SRS WOW audio technology

## Digital Signal Processor Specification

- 24bit Fixed-point Digital Signal Processing

- Maximum Clock Frequency : 38MHz

- Digital Audio Interface : 2 Input ports / 1 Output port

- Digital Audio Format : I<sup>2</sup>S 24bit, Left-Justified, Right-Justified, BCK : 32Fs / 64Fs

**Digital Audio Processor for TV**

- Master / Slave Mode

- Master Mode MCK

- : 1/2 fclk, 1/3 fclk ex. MCK = 384Fs(1/2) or MCK = 256Fs(1/3) at fclk=768Fs

- Two kinds of micro computer interface

- I<sup>2</sup>C Bus (standard-mode/100Kbps)

- 4-Wire Serial Bus (4-Wire: Clock, Enable, Input data, Output data)

- Power Supply : DSP Core : 2.5V I/O interface: 2.5V (+3.3V tolerant)

- Package

The detail hardware specification of the NJU26103 is described in the "NJU26100 Series Hardware Data Sheet". In respect to software commands, request NJR.

New Japan Radio Co., Ltd.

NJU26103

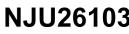

## DSP Block Diagram

#### Fig.1 NJU26103 Block Diagram

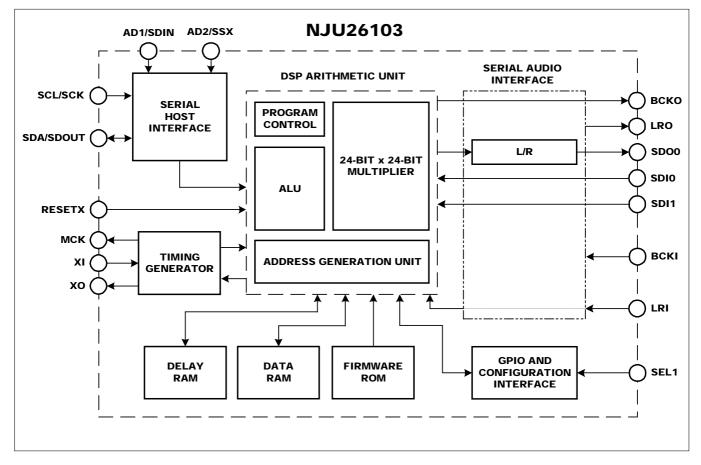

# **DSP** Function Diagram

### Fig.2 NJU26103 Function Diagram

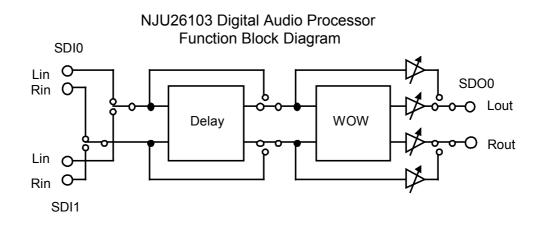

# Pin Configuration

## Pin Description

#### **Table1 Pin Description**

| TUN |           |     |                                                  |     |                         |     |                          |  |

|-----|-----------|-----|--------------------------------------------------|-----|-------------------------|-----|--------------------------|--|

| No. | Symbol    | I/O | Description                                      | No. | Symbol                  | I/O | Description              |  |

| 1   | TEST0     | 0   | OPEN 17 VDDC P Core Power Sup                    |     | Core Power Supply +2.5V |     |                          |  |

| 2   | TEST1     | 0   | OPEN                                             | 18  | VDDC                    | Р   | Core Power Supply +2.5V  |  |

| 3   | SDO0      | 0   | Audio Data Output L/R                            | 19  | VSSC                    | G   | Core GND                 |  |

| 4   | SEL1      | 1   | Select I <sup>2</sup> C(L) or 20 VSSC G Core GND |     | Core GND                |     |                          |  |

|     |           |     | Serial bus(H)                                    |     |                         |     |                          |  |

| 5   | SCL/SCK   | 1   | I <sup>2</sup> C Clock / Serial Clock            | 21  | VDDR                    | Р   | I/O Power Supply +2.5V   |  |

| 6   | SDA/SDOUT | 10  | I <sup>2</sup> C I/O / Serial Output             | 22  | VDDR                    | Р   | I/O Power Supply +2.5V   |  |

| 7   | AD1/SDIN  | 1   | I <sup>2</sup> C Address / Serial Input          | 23  | VSSR                    | G   | I/O GND                  |  |

| 8   | AD2/SSX   | 1   | I <sup>2</sup> C Address / Serial Enable         | 24  | VSSR                    | G   | I/O GND                  |  |

| 9   | VDDO      | Ρ   | OSC Power Supply +2.5V                           | 25  | SDI0                    |     | Audio Data Input 0 L/R   |  |

| 10  | XI        |     | X'tal Clock Input                                | 26  | SDI1                    |     | Audio Data Input 1 L / R |  |

| 11  | XO        | 0   | X'tal Clock Output                               | 27  | TEST 3                  | Ι   | GND                      |  |

| 12  | VSSO      | G   | OSC GND                                          | 28  | LRI                     | 1   | LR Clock Input           |  |

| 13  | RESETX    |     | RESET                                            | 29  | BCKI                    | 1   | Bit Clock Input          |  |

| 14  | VDDC      | Ρ   | Core Power Supply +2.5V                          | 30  | MCK                     | 0   | Master Clock Output      |  |

| 15  | VSSC      | G   | Core GND                                         | 31  | BCKO                    | 0   | Bit Clock Output         |  |

| 16  | TEST2     | 10  | OPEN                                             | 32  | LRO                     | 0   | LR Clock Output          |  |

|     |           |     |                                                  |     |                         |     |                          |  |

X I: Input, O: Output, IO: Bi-directional, P: +Power, G: GND

New Japan Radio Co., Ltd.

# Audio Data Interface

The NJU26103 audio interface provides Industry standard serial data formats of I<sup>2</sup>S, MSB-first left-justified or MSB-first right-justified. The NJU26103 audio interface provides two data inputs, SDI0 and SDI1, and one data output, SDO0. The input serial data is selected by the firmaware command.

#### Table 2 Serial Audio Input Pin

| Symbol | Pin No. | Description              |

|--------|---------|--------------------------|

| SDI0   | 25      | Sound Data Input 0 L / R |

| SDI1   | 26      | Sound Data Input 1 L / R |

### Table 3 Serial Audio Output Pin

| Symbol | Pin No. | Description         |

|--------|---------|---------------------|

| SDO0   | 3       | Sound Data Output 0 |

# ■ I<sup>2</sup>C address

AD1 and AD2 pins are used to configure the seven-bit SLAVE address of the serial host interface. These pins offer additional flexibility to SLAVE address. 4 addresses could be chosen by AD1 and AD2-pin. The AD1 and AD2-pin addresses are decided by the connections of AD1 and AD2-pin. The AD1 and AD2 addresses should be the same level as AD1 and AD2-pin connections.

### Table 4I<sup>2</sup>C Bus SLAVE Address

|      |      | 0    |      |      |       |                   |      |

|------|------|------|------|------|-------|-------------------|------|

| bit7 | bit6 | bit5 | bit4 | Bit3 | bit2  | bit1              | bit0 |

| 0    | 0    | 1    | 1    | 1    | AD2*1 | AD1* <sup>1</sup> | R/Ŵ  |

\*1 AD1 or AD2 address is 0 when AD1 or AD2-pin is "L". AD1 or AD2 address is 1 when AD1 or AD2-pin is "H".

The detail I<sup>2</sup>C bus timing of the NJU26103 is described in the "NJU26100 Series Hardware Data Sheet".

## Firmware Command Table

The NJU26103 can be controlled by host processor vie  $I^2C$  bus or 4-Wire serial bus interface. The following table summarizes the available user commands.

| No. | Command          | Command Description                                 |  |  |  |  |

|-----|------------------|-----------------------------------------------------|--|--|--|--|

| 1   | Fs               | Select the sampling frequency : 32/44.1/48KHz       |  |  |  |  |

| 2   | Input Select     | Select digital audio input                          |  |  |  |  |

| 3   | Mode Select      | Select mode : Mute, Thru, WOW                       |  |  |  |  |

| 4   | WOW              | Select WOW parameters : Bit rate, Focus, Input mode |  |  |  |  |

| 5   | TruBass          | Select TruBass Speaker size                         |  |  |  |  |

| 6   | Delay Time       | Set Delay time                                      |  |  |  |  |

| 7   | Program Mode     | Select mode : Stereo, TruBass, Focus, Delay         |  |  |  |  |

| 8   | Through Output   | Trim Through output level                           |  |  |  |  |

| 9   | WOW Output Trim  | Trim WOW output level                               |  |  |  |  |

| 10  | TruBass          | TruBass Control                                     |  |  |  |  |

| 11  | Stereo Width     | Stereo Width Control                                |  |  |  |  |

| 12  | System State     | Set System parameters : Digital Audio Format        |  |  |  |  |

| 13  | Firmware Version | Check Firmware Version                              |  |  |  |  |

| 14  | NOP              | Check DSP condition                                 |  |  |  |  |

#### Table 5 NJU26103 Command List

## License Information

1. The SRS technology right incorporated in the NJU26103 are owned by SRS Labs, a U.S. Corporation and licensed to New Japan Radio Co., Ltd. SRS is protected under U.S. and foreign patents issued and / or pending. SRS, WOW and the ••• are trademarks of SRS Labs, Inc. in the United States and selected foreign countries. Neither the purchase of the NJU26103, nor the corresponding sale of audio enhancement equipment conveys the right to sell commercialized recordings made with any SRS technology.

SRS Labs requires that all users of the NJU26103 must enter into a license agreement directly with SRS Labs if the royalty is not Included in the purchase price. SRS Labs also requires any users to comply with all rules and regulations as outlined in the SRS Trademark Usage Manual.

For further information, please contact:

SRS Labs, Inc. 2909 Daimler Street. Santa Ana, CA 92705 USA

Tel: 949-442-1070 Fax: 949-852-1099 http://www.srslabs.com

2 Purchase of I<sup>2</sup>C components of New Japan Radio Co., Ltd or one of sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard specification as defined by Philips.

| [CAUTION] |

|-----------|

|-----------|

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

Version V3.0